Specifications

Important

Unless otherwise stated, all specifications apply after 30 minutes of

instrument warm-up.

For measurements in which high gate fidelity is crucial, it is

highly recommended to enable all required outputs and wait for 2 hours

after powering on the instrument.

Important

Important changes in the specification parameters are explicitly

mentioned in the revision history of this document.

General Specifications

Table 1: General and storage

Parameter

Min

Typ

Max

storage temperature

–25 °C

-

65 °C

storage relative humidity (non-condensing)

-

-

95%

operating temperature

5 °C

-

40 °C

operating relative humidity (non-condensing)

-

-

90%

specification temperature

18 °C

-

28 °C

power consumption

-

-

300 W

operating environment

IEC61010, indoor location, installation category II, pollution degree 2

operating altitude

up to 2000 meters

power inlet fuses

250 V, 2 A, fast acting, 5 x 20 mm

power supply AC line

100-240 V (±10%), 50/60 Hz

dimensions (width x depth x height)

45.0 × 39.7 × 13.2 cm (no handle), 17.7 × 15.6 × 5.2 inch, 19 inch rack compatible

weight

15 kg (33 lb)

recommended calibration interval

2 years

Table 2: Maximum ratings

Parameter

Min

Typ

Max

damage threshold Out

-

-

+30 dBm

damage threshold Mark Out

–0.7 V

-

+4 V

damage threshold Trig In (1 kΩ input impedance)

–11 V

-

+11 V

damage threshold Trig In (50 Ω input impedance)

–6 V

-

+6 V

damage threshold Aux In (DC)

-10 V

-

+10 V

damage threshold Aux In (AC)

-

-

+20 dBm

damage threshold External Clk In (DC)

–3 V

-

+3 V

damage threshold External Clk In (AC, with DC offset 0 V)

-

-

+13.5 dBm

damage threshold External Clk Out (DC)

–3 V

-

+3 V

MDS In / Out

–0.7 V

-

+4 V

DIO In / Out in default configuration 3.3 V CMOS/TTL

–0.7 V

-

+4 V

torque limit front panel SMA connectors

-

-

0.5 Nm

torque limit back panel SMA connectors

-

-

1.0 Nm

Table 3: Host computer requirements

Parameter

Description

supported Windows operating systems

Windows 10, 11 on x86-64

supported macOS operating systems

macOS 10.11+ on x86-64 and ARMv8

supported Linux distributions

GNU/Linux (Ubuntu 14.04+, CentOS 7+, Debian 8+) on x86-64 and ARMv8

supported processors

x86-64 (Intel, AMD), ARMv8 (e.g., Raspberry Pi 4 and newer, Apple M-series)

Analog Interface Specifications

Table 4: Signal Outputs

Parameter Details Min Typ Max

connectors - SMA, front panel single-ended impedance - - 50 Ω - coupling LF path DC RF path AC

synthesizers SHFSG2+ and SHFSG4+ One per channel SHFSG8+ One per channel pair

synthesizer frequency range 0.6-8 GHz instantaneous bandwidth (–3dB) RF path ±500 MHz LF path DC - 2500 MHz

total frequency range DC - 8.5 GHz range RF path, into 50 Ω -30 dBm - +10 dBm LF path, into 50 Ω -30 dBm - +5 dBm

output level accuracy into 50 Ω - ±(1 dBm of setting) - output level temperature drift - 0.15 dB/°C - D/A converter vertical resolution - 14 bit D/A converter sampling rate after internal x3 interpolation 6 GSa/s voltage spectral noise density RF path, 10 dBm range - -143 dBm/Hz - phase noise RF path, 5 GHz, 10 kHz offset frequency - -110 dBc/Hz - RF path, 5 GHz, 10 MHz offset frequency - -138 dBc/Hz -

spurious free dynamic range (excluding harmonics) RF path, 10 dBm range, - 48 dBc - worst harmonic component 10 dBm range 1 GHz - -40 dBc - 4 GHz - -40 dBc -

6 GHz - -38 dBc -

8 GHz - -36 dBc -

Table 5: Time Domain Output Characteristics

Parameter Details Min Typ Max

skew adjustment resolution - 500 ps

Table 6: Marker Outputs & Trigger Inputs

Parameter

Details

Min

Typ

Max

marker outputs

-

1 per channel

marker outputs connector

-

SMA, front panel single-ended

marker output high voltage

-

-

3.3 V

-

marker output low voltage

-

-

0 V

-

marker output impedance

-

-

50 Ω

-

marker output rise time 20% to 80%

-

-

300 ps

-

trigger inputs

-

1 per channel

trigger inputs connector

-

SMA, front panel single-ended

trigger input impedance

-

50 Ω / 1 kΩ

trigger input voltage range

50 Ω impedance

–5 V

-

5 V

1 kΩ impedance

–10 V

-

10 V

trigger input threshold range

50 Ω impedance

–5 V

-

5 V

1 kΩ impedance

–10 V

-

10 V

trigger input threshold resolution

-

-

< 0.4 mV

-

trigger input threshold hysteresis

-

-

> 60 mV

-

Table 7: Other Inputs and Outputs

Parameter

Details

min

Typ

Max

reference clock input

-

SMA on back panel

reference clock input impedance

-

50 Ω, AC coupled

reference clock input frequency

-

10 / 100 MHz

reference clock input amplitude

10 MHz

-4 dBm

-

+13 dBm

100 MHz

–5 dBm

-

+13 dBm

reference clock output

-

SMA on back panel

reference clock output impedance

50 Ω, AC coupled

reference clock output amplitude

into 50 Ω

2 Vpp

-

5 Vpp

reference clock output frequency

10/100 MHz

reference clock output jitter

derived from integrated phase noise measurement (12 kHz to 20 MHz offset frequency)

-

280 fs RMS

-

Table 8: Oscillator and Clocks

Parameter

Details

Min

Typ

Max

internal clock type

-

OCXO

internal clock long term accuracy / aging

-

-

-

±0.3 ppm/year

internal clock short term stability (1 s)

-

-

-

±0.05 ppm

internal clock initial accuracy

-

-

-

±0.5 ppm

internal clock temperature stability

–20°C to 70°C

-

-

±0.5 ppm

internal clock phase noise

offset 100 Hz

-

–135 dBc/Hz

-

offset 1 kHz

-

–157 dBc/Hz

-

Table 9: Waveform Generation

Parameter

Details

Specification

number of AWG cores

for SHFSG+ base version

1 per channel

for SHFSG+ with SHFSG-RTR

8 total

AWG sampling rate

dual-channel

2 GSa/s

waveform memory per output channel

-

96 kSa

sequence length

-

32 kInstructions instructions per core

waveform granularity

-

16 samples

minimum waveform length

-

16 samples (with command table)

sequencer clock frequency

-

250 MHz

Digital Interface Specifications

Table 10: Digital Interfaces

Parameter

Description

host computer connection

USB 3.0, 1.6 Gbit/s (1 communication, 1 maintenance)

1GbE, LAN / Ethernet, 1 Gbit/s

DIO port

4 x 8 bit, general purpose digital input/output port, 3.3 V TTL specification

ZSync peripheral port

connector for ZI proprietary bus to communicate with external peripherals

DIO Port

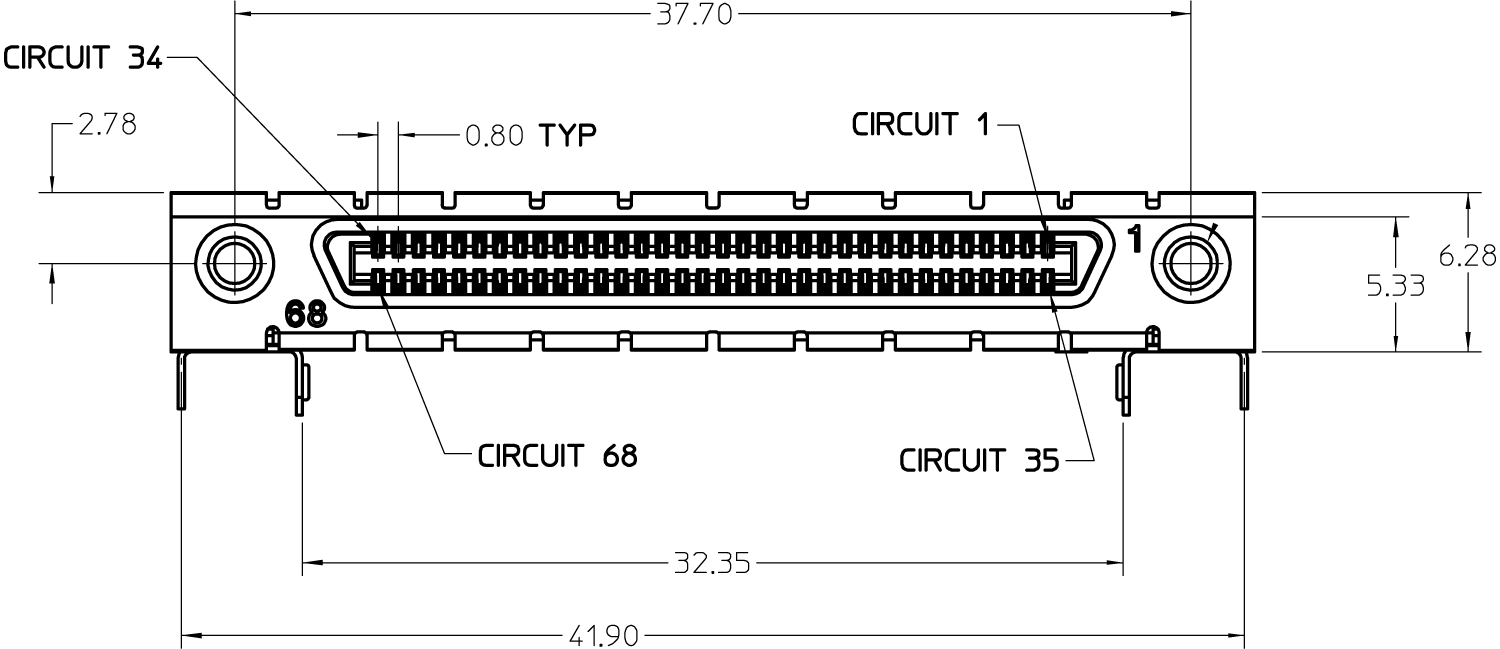

The DIO port is a VHDCI 68 pin connector as introduced by the SPI-3

document of the SCSI-3 specification. It is a female connector that

requires a 32 mm wide male connector. The interface standard is

switchable between LVDS (low-voltage differential signalling) and

LVCMOS/LVTTL. The DIO port features 32 user-controlled bits that can all

be configured byte-wise as inputs or outputs in LVCMOS/LVTTL mode,

whereas in LVDS mode, half of the bits are always configured as inputs.

For more specifics on how the user-definable pins can be set.

Figure 1: DIO HD 68 pin connector

Table 11: Electrical Specifications

Parameter

Details

Min

Typ

Max

supported DIO interface standards

-

LVCMOS/LVTTL (single-ended, 3.3 V); LVDS (differential)

high-level input voltage VIH

LVCMOS/LVTTL

2.0 V

-

-

low-level input voltage VIL

LVCMOS/LVTTL

-

-

0.8 V

high-level output voltage VOH

LVCMOS/LVTTL

2.6 V

-

-

low-level output voltage VOL

LVCMOS/LVTTL

-

-

0.4 V

high-level output current IOH (sourcing)

LVCMOS/LVTTL

-

-

12 mA

low-level output current IOL (sinking)

LVCMOS/LVTTL

-

-

12 mA

input differential voltage VID

LVDS

100 mV

-

600 mV

input common-mode voltage VICM

LVDS

0.3 V

-

2.35 V

output differential voltage VOD

LVDS

247 mV

-

454 mV

output common-mode voltage VOCM

LVDS

1.125 V

-

1.375 V

Table 12: DIO Pin Assignment in LVCMOS/LVTTL Mode

Pin

Name

Description

68

unused

leave unconnected

67

unused

leave unconnected

66 .. 59

DIO[31:24]

digital input or output byte (set by user)

58 .. 51

DIO[23:16]

digital input or output byte (set by user)

50 .. 43

DIO[15:8]

digital input or output byte (set by user)

42 .. 35

DIO[7:0]

digital input or output byte (set by user)

34

GND

digital ground

33

unused

leave unconnected

32 .. 1

GND

digital ground

Table 13: DIO Pin Assignment in LVDS Mode

Pin

Name

Description

68

unused

leave unconnected

67

unused

leave unconnected

66 .. 59

DI+[31:24]

digital input byte

58 .. 51

DI+[23:16]

digital input byte

50 .. 43

DIO+[15:8]

digital input or output byte (set by user)

42 .. 35

DIO+[7:0]

digital input or output byte (set by user)

34

unused

leave unconnected

33

unused

leave unconnected

32 .. 25

DI–[31:24]

digital input byte

24 .. 17

DI–[23:16]

digital input byte

16 .. 9

DIO–[15:8]

digital input or output byte (set by user)

8 .. 1

DIO–[7:0]

digital input or output byte (set by user)